This project is coded in C and helped me develop a good understanding of how a computer's cache memory works

and how different configurations affect its performance and efficiency. The problem is the implement a program that is given

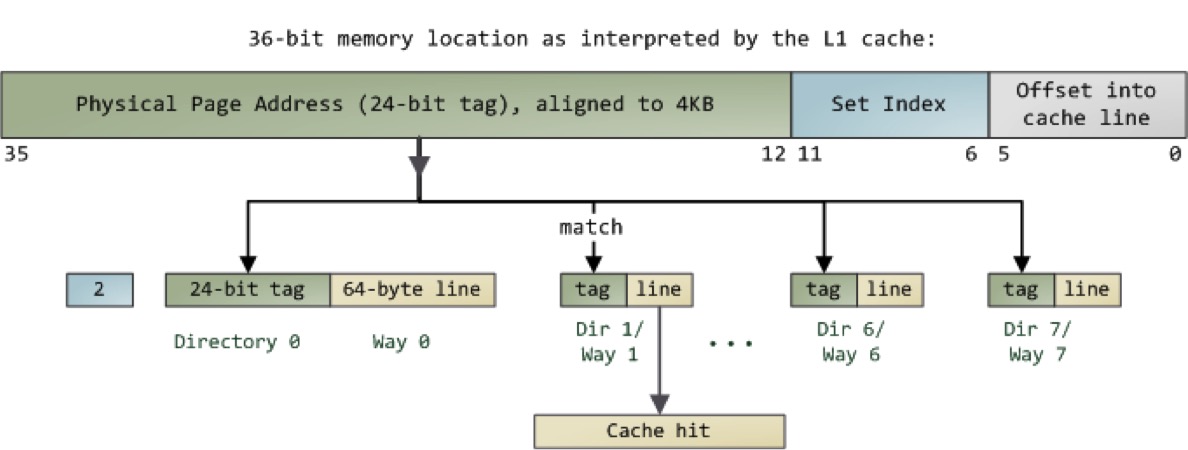

a set of parameters such as: cache size, associativity, block size, replacement policy, write policy, and a trace file which contains

a long list of memory read and write commands in the following form:

0x804ae19: W 0x9cb32e0

0x804ae1c: R 0x9cb32e4

0x804ae1c: W 0x9cb32e4

0x804ae10: R 0xbf8ef498

where the first address represents the and the program simulates these commands based on the cache configurations and outputs

the number of memory reads & writes the cache has to perform to do the list of actions and the number of cache hits & misses,

which are both indicative of the cache's performance under those configurations.

Feel free to download the project on GitHub and try it out yourself